# LECTURE NOTES ON DIGITAL ELECTRONICS & MICROPROCESSOR

### PREPARED BY -ER. JYOTISMITA GHADEI

### VISION OF THE DEPARTMENT-

★ To be a center of excellence in the field of E&TC Engineering by providing quality technical education.

### MISSION OF THE DEPARTMENT-

- To create an excellent teaching learning environment for making the students acquire the knowledge needed.

- To inculcate self-learning attitude, entrepreneurial skill.

- To impart knowledge required for recent and advanced engineering.

### PROGRAM EDUCATIONAL OBJECTIVE (PEO)-

- Recognize and apply the acquired fundamental knowledge in basic science and mathematics in solving E&TC Engineering problems.

- To gain employment in public and private sector organization.

- Involve in higher study and career enhancement.

### PROGRAM SPECIFIC OUTCOME (PSO)-

- To design, test and troubleshoot the simple analog and digital circuits.

- An ability to solve complex E&TC Engineering problems using various tools i.e. hardware and software.

- To pursue higher studies or get placed in various industries.

### COURSE OUTCOME (CO)-

- After the completion of the course the students will be able to

- Apply the knowledge of Boolean algebra and K-map for logic function minimization.

- Design combinational circuits and sequential circuits and implement them with logic gates.

- Implement logic gates by using different logic family.

- Apply the fundamental knowledge of Analog and Digital Electronics for analog version and vice versa.

- Analyze and apply the nomenclature and technology of memory devices and various types registers in digital circuits for real world application.

### TH.3 DIGITAL ELECTRONICS & MICROPROCESSOR

| Name of the Course: Diploma in Electrical Engineering |                                     |                           |    |  |  |

|-------------------------------------------------------|-------------------------------------|---------------------------|----|--|--|

| Course code: Th.3 Semester 5th                        |                                     |                           |    |  |  |

| Total Period:                                         | Total Period: 75 Examination 3 Hrs. |                           |    |  |  |

| Theory periods:                                       | 5P / week                           | Internal Assessment:      | 20 |  |  |

| Tutorial:                                             |                                     | End Semester Examination: | 80 |  |  |

| Maximum marks:                                        | 100                                 |                           |    |  |  |

### A. RATIONALE

The tremendous power and usefulness of digital electronics can be seen from the wide variety of industrial and consumer products, such as automated industrial machinery, computers, microprocessors, pocket calculators, digital watches and clocks, TV games, etc., Which are based on the principles of digital electronics? The years of applications of digital electronics have been increasing every day. In fact, digital systems have invaded all walks of life. This subject will very much helpful for student to understand clearly about the developmental concept of digital devices.

### **B. OBJECTIVES**

On comprehend of the subject, the student will able to

- 1. Comprehend the systems and codes.

- 2. Familiar with logic gates.

- 3. Realize logic expressions using gates.

- 4. Construct and verify the operation of arithmetic & logic circuits 5. Understand and appreciate the relevance of combinational circuits.

- 6. Know various logic families & flops.

- 7. Architecture & different instructions of 8085 microprocessor.

- 8. Assembly language programs and write programs & functions of the interfacing chips like 8255, 8259, 8259 etc.

### C. TOPIC WISE DISTRIBUTION OF PERIODS

| SI. No. | Topics                        |    | Periods |

|---------|-------------------------------|----|---------|

| 1.      | Basics Of Digital Electronics | 15 |         |

| 2.      | Combinational Logic Circuits  | 15 |         |

| 3.      | Sequential Logic Circuits 15  |    |         |

| 4.      | 8085 Microprocessor 20        |    |         |

| 5.      | Interfacing And Support Chips | 10 |         |

|         | Total                         |    | 75      |

### **COURSE CONTENT IN TERMS OF SPECIFIC OBJECTIVES**

### 1. BASICS OF DIGITAL ELECTRONICS

- 1.1 Binary, Octal, Hexadecimal number systems and compare with Decimal system.

- 1.2 Binary addition, subtraction, Multiplication and Division.

- 1.3 1's complement and 2's complement numbers for a binary number

- 1.4 Subtraction of binary numbers in 2's complement method.

- 1.5 Use of weighted and Un-weighted codes & write Binary equivalent number for a number in 8421, Excess-3 and Gray Code and vice-versa.

- 1.6 Importance of parity Bit.

- 1.7 Logic Gates: AND, OR, NOT, NAND, NOR and EX-OR gates with truth table.

- 1.8 Realize AND, OR, NOT operations using NAND, NOR gates.

- 1.9 Different postulates and De-Morgan's theorems in Boolean algebra.

- 1.10 Use Of Boolean Algebra For Simplification Of Logic Expression

- 1.11 Karnaugh Map For 2,3,4 Variable, Simplification Of SOP And POS Logic Expression Using K-Map.

### 2. COMBINATIONAL LOGIC CIRCUITS

- 2.1 Give the concept of combinational logic circuits.

- 2.2 Half adder circuit and verify its functionality using truth table.

- 2.3 Realize a Half-adder using NAND gates only and NOR gates only.

- 2.4 Full adder circuit and explain its operation with truth table.

- 2.5 Realize full-adder using two Half-adders and an OR gate and write truth table 2.6 Full subtractor circuit and explain its operation with truth table. 2.7 Operation of 4 X 1 Multiplexers and 1 X 4 demultiplexer 2.8 Working of Binary-Decimal Encoder & 3 X 8 Decoder.

- 2.9 Working of Two bit magnitude comparator.

### 3. SEQUENTIAL LOGIC CIRCUITS

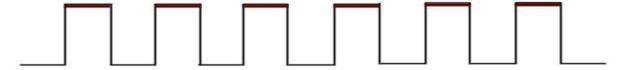

- 3.1 Give the idea of Sequential logic circuits.

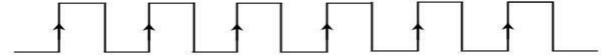

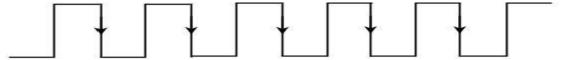

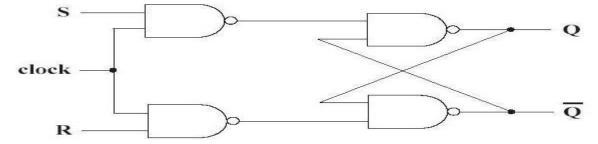

- 3.2 State the necessity of clock and give the concept of level clocking and edge triggering,3.3 Clocked SR flip flop with preset and clear inputs.

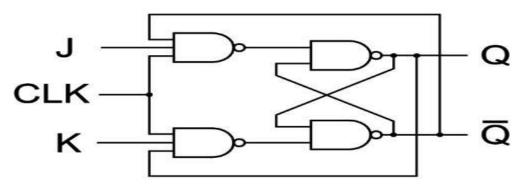

- 3.5 Construct level clocked JK flip flop using S-R flip-flop and explain with truth table

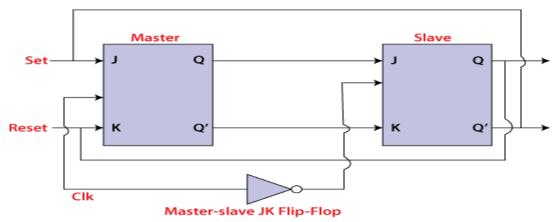

- 3.6 Concept of race around condition and study of master slave JK flip flop.

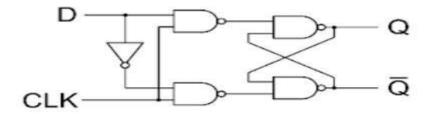

- 3.7 Give the truth tables of edge triggered D and T flip flops and draw their symbols.

- 3.8 Applications of flip flops.

- 3.9 Define modulus of a counter

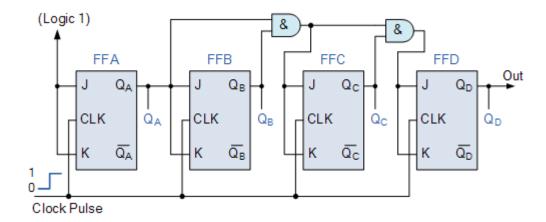

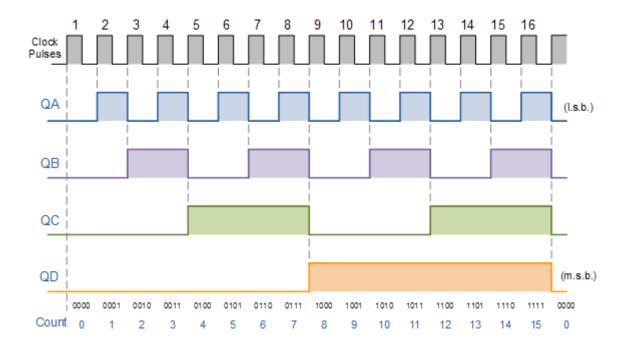

- 3.10 4-bit asynchronous counter and its timing diagram.

- 3.11 Asynchronous decade counter.

- 3.12 4-bit synchronous counter.

- 3.13 Distinguish between synchronous and asynchronous counters.

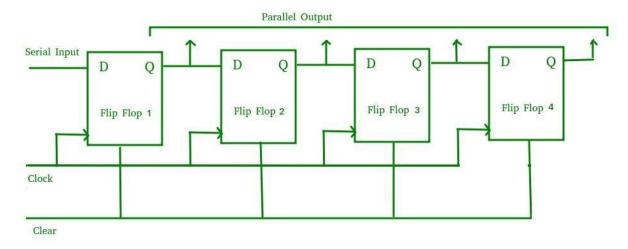

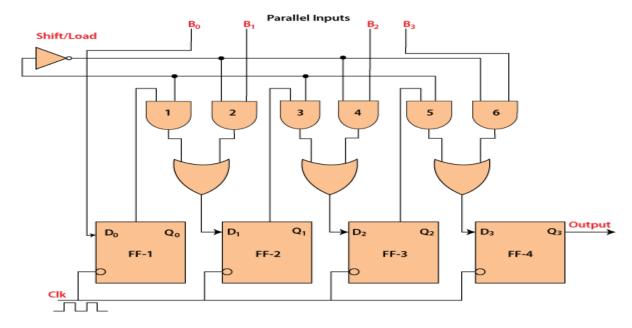

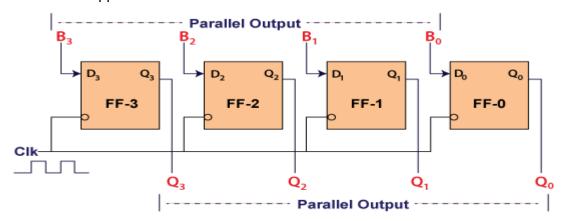

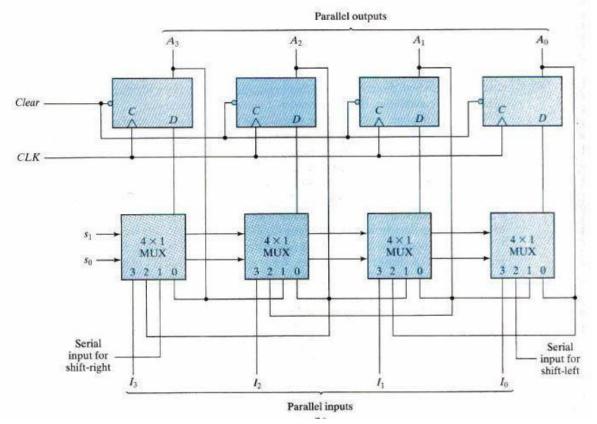

- 3.14 State the need for a Register and list the four types of registers.

- 3.15 Working of SISO, SIPO, PISO, PIPO Register with truth table using flip flop.

### 4. 8085 MICROPROCESSOR

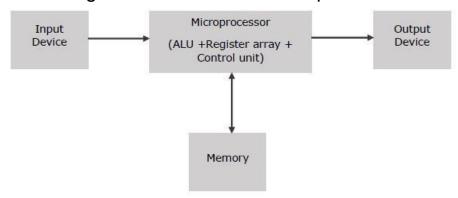

- 4.1 Introduction to Microprocessors, Microcomputers

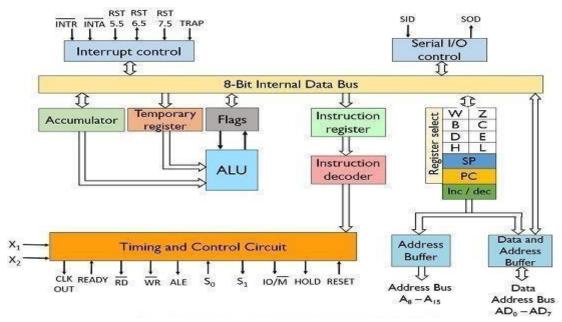

- 4.2 Architecture of Intel 8085A Microprocessor and description of each block.

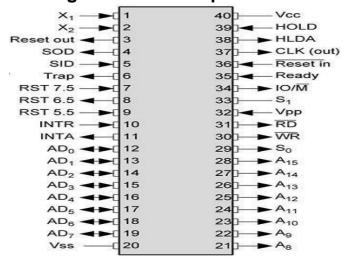

- 4.3 Pin diagram and description.

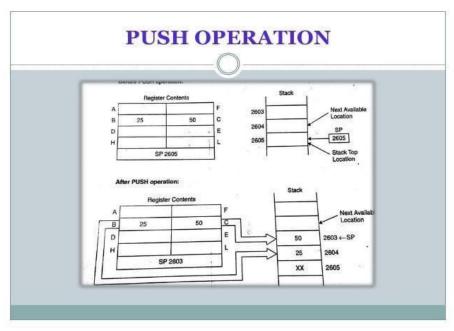

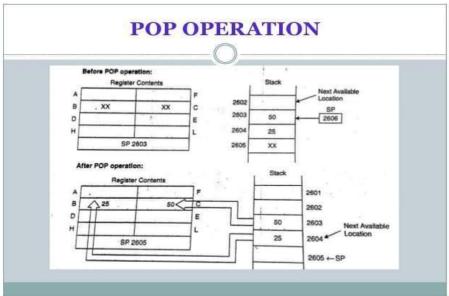

- 4.4 Stack, Stack pointer & stack top

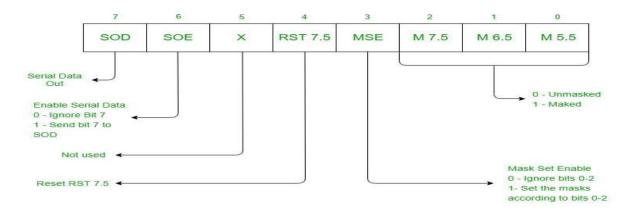

- 4.5 Interrupts

- 4.6 Opcode & Operand,

- 4.7 Differentiate between one byte, two byte & three byte instruction with example.

- 4.8 Instruction set of 8085 example

- 4.9 Addressing mode

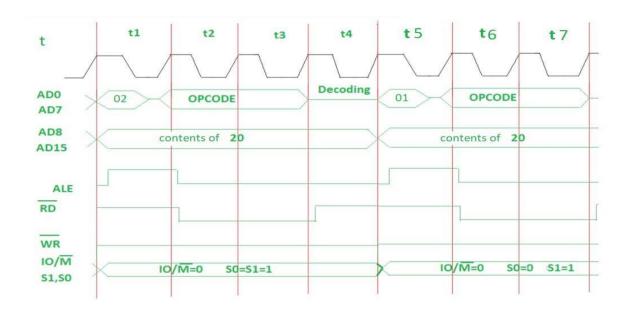

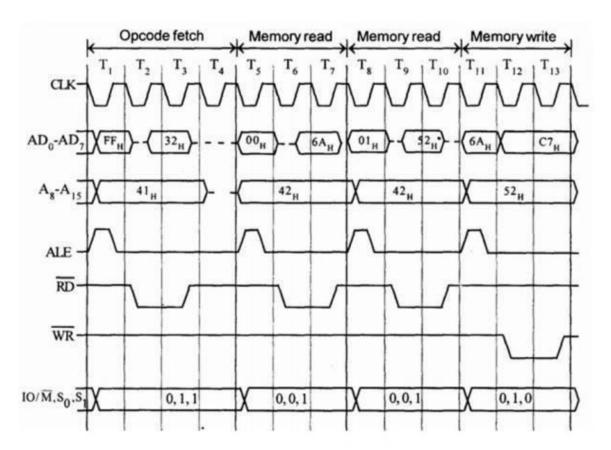

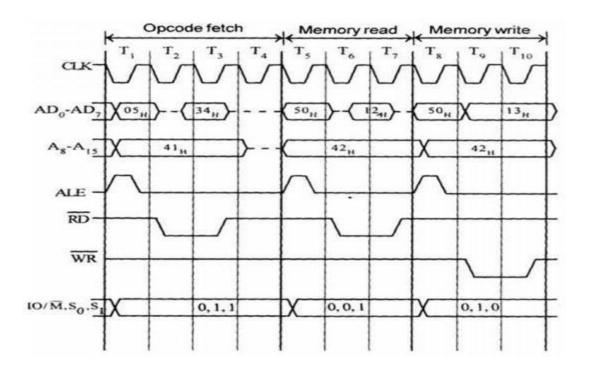

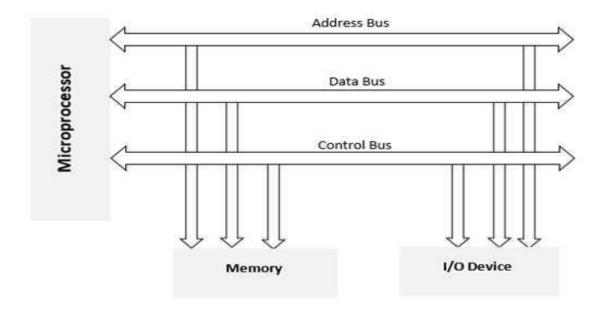

- 4.10 Fetch Cycle, Machine Cycle, Instruction Cycle, T-State

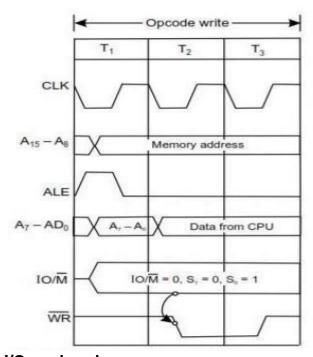

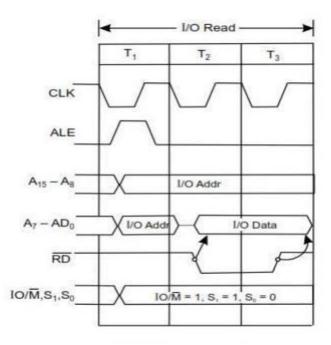

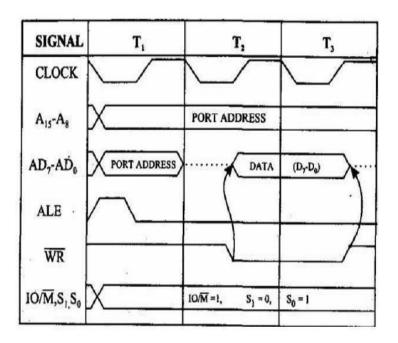

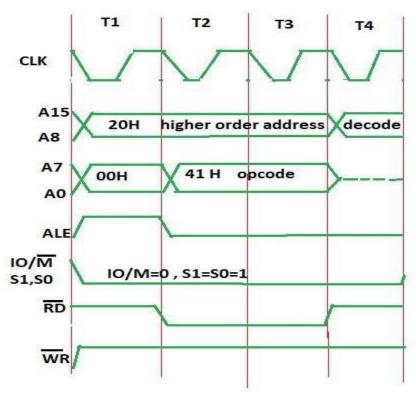

- 4.11 Timing Diagram for memory read, memory write, I/O read, I/O write

- 4.12 Timing Diagram for 8085 instruction

- 4.13 Counter and time delay.

- 4. 14 Simple assembly language programming of 8085.

### 5. INTERFACING AND SUPPORT CHIPS

- 5.1 Basic Interfacing Concepts, Memory mapping & I/O mapping

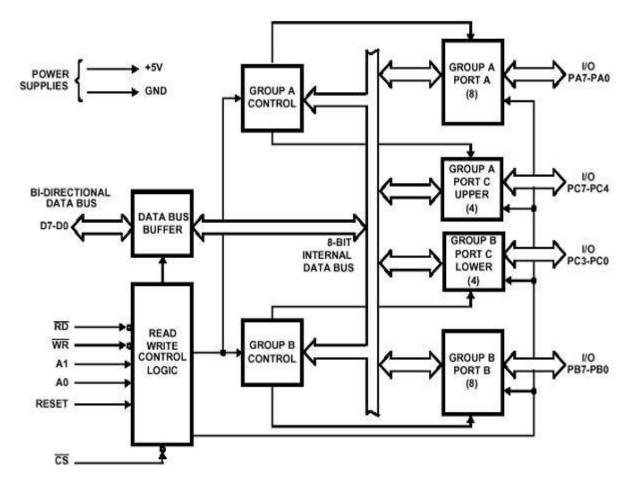

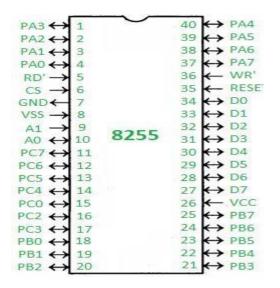

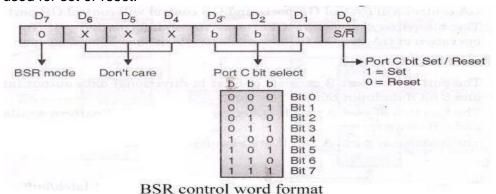

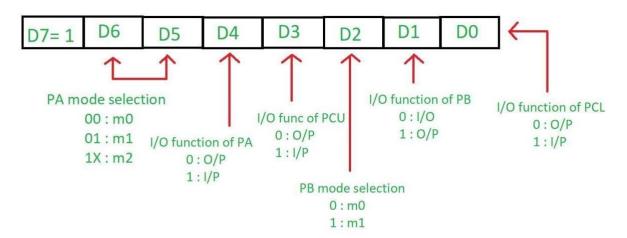

- 5.2 Functional block diagram and description of each block of Programmable peripheral interface Intel 8255,

- 5.3 Application using 8255: Seven segment LED display, Square wave generator,

Traffic light Controller

## DIGITAL ELECTRONICS AND MICROPROCESSOR 5<sup>TH</sup> SEMESTER ELECTRICAL ENGINEERING

### **UNIT-1BASICS OF DIGITAL ELECTRONICS**

### **Introduction to Digital Electronics:**

- Digital electronics deals with the electronic manipulation of numbers, or with the manipulation of varying quantities by means of numbers.

- Because it is convenient to do so, today's digital systems deal only with the numbers 'zero' and 'one', because they can be represented easily by 'off and 'on' within a circuit.

- This is not the limitation it might seem, for the binary system of counting can be used to represent any number that we can represent with the usual decimal (0 to 9) system that we use in everyday life.

- Digital Electronics is very important in today's life because if digital circuits compared to analog circuits are that signals represented digitally can be transmitted without degradation due to noise.

### **Advantages of Digital Circuits**

- · High accuracy and programmability

- · Storage of digital data is easy

- · Immune to noise

- Can be implemented in the form of integrated circuits (ICs)

- Greater reliability and flexibility

### **Disadvantages of Digital Circuits**

- Expensive

- Operate on digital signals only

- Complex circuitry

### **Applications of Digital Circuits**

- Mobile Phones, Calculators and Digital Computers

- Radios and communication Devices

- Signal Generator

- Smart Card

- Cathode Ray Oscilloscope (CRO)

- Analog to digital converters (ADC)

- · Digital to analog converters (DAC), etc.

### Number system:

- A number system is defined as a system of writing to express numbers.

- It is the mathematical notation for representing numbers of a given set by using digits or other symbols in a consistent manner.

- It provides a unique representation of every number and represents the arithmetic and algebraic structure of the figures.

- It also allows us to operate arithmetic operations like addition, subtraction and division. The value of any digit in a number can be determined by:

- · The digit

- Its position in the number

The base of the number system Types of number system:

There are various types of number systems in mathematics. The four most common number system types are:

- Decimal number system (Base- 10)

- Binary number system (Base- 2)

- Octal number system (Base-8)

- Hexadecimal number system (Base- 16) A number N in base or radix 'r' can be written as:

$$(N)_b = d_{n-1} d_{n-2} - - - - d_1 d_0 \cdot d_{-1} d_{-2} - - - - d_{-m}$$

In the above, dn-1 to d0 is the integer part, then follows a radix point, and then d-1 to d-m is the fractional part.

$D_{n-1} = Most significant bit (MSB) d_{-m}$

= Least significant bit (LSB)

### **Decimal number system:**

The base or radix of Decimal number system is 10. So, the numbers ranging from 0 to 9 are used in this number system. Mathematically, we can write it as

$$1358.246 = (1 \times 10^{3}) + (3 \times 10^{2}) + (5 \times 10^{1}) + (8 \times 10^{0}) + (2 \times 10^{-1}) + (4 \times 10^{-2}) + (6 \times 10^{-3})$$

### **Binary number system:**

All digital circuits and systems use this binary number system. The base or radix of this number system is 2. So, the numbers 0 and 1 are used in this number system.

Mathematically, we can write it as

$$1101.011 = (1 \times 2^{3}) + (1 \times 2^{2}) + (0 \times 2^{1}) + (1 \times 2^{0}) + (0 \times 2^{-1}) + (1 \times 2^{-2}) + (1 \times 2^{-3})$$

### Octal number system:

The base or radix of octal number system is 8. So, the numbers ranging from 0 to 7 are used in this number system.

Mathematically, we can write it as

$$1457.236 = (1 \times 8^{3}) + (4 \times 8^{2}) + (5 \times 8^{1}) + (7 \times 8^{0}) + (2 \times 8^{-1}) + (3 \times 8^{-2}) + (6 \times 8^{-3})$$

### **Hexadecimal number system:**

The base or radix of Hexa-decimal number system is 16. So, the numbers ranging from 0 to 9 and the letters from A to F are used in this number system. The decimal equivalent of Hexadecimal digits from A to F are 10 to 15.

Mathematically, we can write it as

$$1A05.2C4 = (1 \times 16^{3}) + (10 \times 16^{2}) + (0 \times 16^{1}) + (5 \times 16^{0}) + (2 \times 16^{-1}) + (12 \times 16^{-2}) + (4 \times 16^{-3})$$

### Conversion from one system to another number system: Decimal number system to other number system:

If the decimal number contains both integer part and fractional part, then convert both the parts of decimal number into another base individually. Steps for converting the decimal number into its equivalent number of any base 'r'-

- Do division of integer part of decimal number and successive quotients with base 'r'

and note down the remainders till the quotient is zero. Consider the remainders in

reverse order to get the integer part of equivalent number of base 'r'. That means, first

and last remainders denote the least significant digit and most significant digit

respectively.

- Do multiplication of fractional part of decimal number and **successive fractions** with base 'r' and note down the carry till the result is zero or the desired number of equivalent digits is obtained. Consider the normal sequence of carry in order to get the fractional part of equivalent number of base 'r'.

### **Decimal to binary:**

Example- (152.25)<sub>10</sub>Step

1: Divide the number 152 and its successive quotients with base 2.

| Operation | Quotient | Remainder |

|-----------|----------|-----------|

| 152/2     | 76       | 0 (LSB)   |

| 76/2      | 38       | 0         |

| 38/2      | 19       | 0         |

| 19/2      | 9        | 1         |

| 9/2       | 4        | 1         |

| 4/2       | 2        | 0         |

| 2/2       | 1        | 0         |

| 1/2       | 0        | 1(MSB)    |

### $(152)_{10} = (10011000)_2$ Step 2:

Now, perform the multiplication of 0.27 and successive fraction with base 2.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.25×2    | 0.50   | 0     |

| 0.50×2 | 0 | 1 |

|--------|---|---|

|--------|---|---|

$(0.25)_{10} = (.01)_2$

### **Decimal to octal:**

Example- (152.25)<sub>10</sub>Step

1:

Divide the number 152 and its successive quotients with base 8.

| Operation | Quotient | Remainder |

|-----------|----------|-----------|

| 152/8     | 19       | 0         |

| 19/8      | 2        | 3         |

| 2/8       | 0        | 2         |

$(152)_{10} = (230)_{8}$

### Step 2:

Now perform the multiplication of 0.25 and successive fraction with base 8.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.25×8    | 0      | 2     |

$(0.25)_{10} = (2)_8$

So, the octal number of the decimal number 152.25 is 230.2 Decimal to

### hexadecimal: Example- (152.25)<sub>10</sub> Step 1:

Divide the number 152 and its successive quotients with base 8.

| Operation | Quotient | Remainder |

|-----------|----------|-----------|

| 152/16    | 9        | 8         |

| 9/16      | 0        | 9         |

$(152)_{10} = (98)_{16}$

Step 2:

Now perform the multiplication of 0.25 and successive fraction with base 16.

| Operation | Result | carry |

|-----------|--------|-------|

| 0.25×16   | 0      | 4     |

$(0.25)_{10} = (4)_{16}$

So, the hexadecimal number of the decimal number 152.25 is 230.4. Binary

### to other number system: Binary to decimal:

The process starts from multiplying the bits of binary number with its corresponding positional weights. And lastly, we add all those products.

Example- (10110.001)<sub>2</sub>

$(10110.001)_2 = (1 \times 2^4) + (0 \times 2^3) + (1 \times 2^2) + (1 \times 2^1) + (0 \times 2^0) + (0 \times 2^{-1}) + (0 \times 2^{-2}) + (1 \times 2^{-3})$

$(10110.001)_2 = (1 \times 16) + (0 \times 8) + (1 \times 4) + (1 \times 2) + (0 \times 1) + (0 \times 1/2) + (0 \times 1/4) + (1 \times 1/8)$

**(10110.001)**<sub>2</sub>=16+0+4+2+0+0+0+0.12

5  $(10110.001)_2=(22.125)_{10}$ Binary to

### octal:

In a binary number, the pair of three bits is equal to one octal digit. Two steps to convert a binary number into an octal number which are as follows:

- In the first step, we have to make the pairs of three bits on both sides of the binary point. If there will be one or two bits left in a pair of three bits pair, we add the required number of zeros on extreme sides.

- In the second step, we write the octal digits corresponding to each pair. **Example-** (11111010111.0011)<sub>2</sub>

- 1. Firstly, we make pairs of three bits on both sides of the binary point. 111 110

101 011.001 1

On the right side of the binary point, the last pair has only one bit. To make it a complete pair of three bits, we added two zeros on the extreme side.

111 110 101 011.001 100 2. Then, we wrote

the octal digits, which correspond to each pair.

### $(111110101011.0011)_2 = (7653.14)_8$ Binary to hexadecimal:

The base numbers of binary and hexadecimal are 2 and 16, respectively. In a binary number, the pair of four bits is equal to one hexadecimal digit. There are also only two steps to convert a binary number into a hexadecimal number which are as follows:

1. In the first step, we have to make the pairs of four bits on both sides of the binary point. If there will be one, two, or three bits left in a pair of four bits pair, we add the required number of zeros on extreme sides.

- 2. In the second step, we write the hexadecimal digits corresponding to each pair. **Example-** (101101011.0011)<sub>2</sub>

- 1. Firstly, we make pairs of four bits on both sides of the binary point.

111 1010 1011.0011

On the left side of the binary point, the first pair has three bits. To make it a complete pair of four bits, add one zero on the extreme side.

0111 1010 1011.0011

2. Then, we write the hexadecimal digits, which correspond to each pair.

### $(011110101011.0011)_2 = (7AB.3)_{16}Octal to other number system:$

### Octal to decimal:

The process starts from multiplying the digits of octal numbers with its corresponding positional weights. And lastly, we add all those products. **Example- (152.25)**<sub>8</sub> **Step 1:**

We multiply each digit of **152.25** with its respective positional weight, and last, we add the products of all the bits with its weight.

$(152.25)_8 = (1 \times 8^2) + (5 \times 8^1) + (2 \times 8^0) + (2 \times 8^{-1}) + (5 \times 8^{-2})$

$(152.25)_8 = 64 + 40 + 2 + (2 \times 1/8) + (5 \times 1/64)$

**(152.25)**<sub>8</sub>=64+40+2+0.25+0.078125

**(152.25)**<sub>8</sub>=106.328125

So, the decimal number of the octal number 152.25 is 106.328125Octal to

### binary:

The process of converting octal to binary is the reverse process of binary to octal. We write the three bits binary code of each octal number digit. **Example- (152.25)**8 We write the three-bit binary digit for 1, 5, 2, and 5.

$(152.25)_8 = (001101010.010101)_2$

So, the binary number of the octal number 152.25 is (001101010.010101)2Octal to

### hexadecimal:

For converting octal to hexadecimal, there are two steps required to perform, which are as follows:

- 1.In the first step, we will find the binary equivalent of number.

- 2.Next, we have to make the pairs of four bits on both sides of the binary point. If there will be one, two, or three bits left in a pair of four bits pair, we add the required number of zeros on extreme sides and write the hexadecimal digits corresponding to each pair. **Example** (152.25)<sub>8</sub>Step 1:

We write the three-bit binary digit for 1, 5, 2, and 5.

$(152.25)_8 = (001101010.010101)_2$

So, the binary number of the octal number 152.25 is (001101010.010101)<sub>2</sub>Step 2:

1. Now, we make pairs of four bits on both sides of the binary point.

0 0110 1010.0101 01

On the left side of the binary point, the first pair has only one digit, and on the right side, the last pair has only two-digit. To make them complete pairs of four bits, add zeros on extreme sides.

0000 0110 1010.0101 0100

2. Now, we write the hexadecimal digits, which correspond to each pair.

$(0000 0110 1010.0101 0100)_2 = (6A.54)_{16}$

**Hexadecimal to other number system:**

### Hexadecimal to decimal:

The process of converting hexadecimal to decimal is the same as binary to decimal. The process starts from multiplying the digits of hexadecimal numbers with its corresponding positional weights. And lastly, we add all those products.

Let's take an example to understand how the conversion is done from hexadecimal to decimal.

### Example- (152A.25)<sub>16</sub>Step

1:

We multiply each digit of **152A.25** with its respective positional weight, and last we add the products of all the bits with its weight.

(152A.25)<sub>16</sub>=

$$(1\times16^3)+(5\times16^2)+(2\times16^1)+(A\times16^0)+(2\times16^{-1})+(5\times16^{-2})$$

(152A.25)<sub>16</sub>= $(1\times4096)+(5\times256)+(2\times16)+(10\times1)+(2\times16^{-1})+(5\times16^{-2})$

(152A.25)<sub>16</sub>= $4096+1280+32+10+(2\times1/16)+(5\times1/256)$

(152A.25)<sub>16</sub>=5418+0.125+0.125

**(152A.25)**<sub>16</sub>=5418.14453125

So, the decimal number of the hexadecimal number 152A.25 is **5418.14453125Hexadecimal to binary:**

The process of converting hexadecimal to binary is the reverse process of binary to hexadecimal. We write the four bits binary code of each hexadecimal number digit. **Example**

### - (152A.25)<sub>16</sub>

We write the four-bit binary digit for 1, 5, A, 2, and 5.

### $(152A.25)_{16} = (0001\ 0101\ 0010\ 1010.0010\ 0101)_2$

So, the binary number of the hexadecimal number 152.25 is (1010100101010.00100101)<sub>2</sub>

| Binary equivalent | Hexadecimal |

|-------------------|-------------|

| 0000              | 0           |

| 0001              | 1           |

| 0010              | 2           |

| 0011              | 3           |

| 0100              | 4           |

| 0101              | 5           |

| 0110              | 6           |

| 0111              | 7           |

| 1000              | 8           |

| 1001              | 9           |

| 1010              | А           |

| 1011              | В           |

| 1100              | С           |

| 1101              | D           |

| 1110              | E           |

| 1111              | F           |

### Hexadecimal to octal:

For converting hexadecimal to octal, there are two steps required to perform, which are as follows:

- 1. In the first step, we will find the binary equivalent of the hexadecimal number.

- 2. Next, we have to make the pairs of three bits on both sides of the binary point. If there will be one or two bits left in a pair of three bits pair, we add the required number of zeros on extreme sides and write the octal digits corresponding to each pair.

### Example- (152A.25)<sub>16</sub>Step

1:

We write the four-bit binary digit for 1, 5, 2, A, and 5.

### $(152A.25)_{16} = (0001\ 0101\ 0010\ 1010.0010\ 0101)_2$

So, the binary number of hexadecimal number 152A.25 is (001101010101010101)<sub>2</sub>Step 2:

- 3. Then, we make pairs of three bits on both sides of the binary point.

- 001 010 100 101 010.001 001 010

- 4. Then, we write the octal digit, which corresponds to each pair.

### $(001010100101010.001001010)_2 = (12452.112)_8$

So, the octal number of the hexadecimal number 152A.25 is **12452.112Arithmetic operation:** Two types of operation that are performed on binary data include arithmetic and logic operations. Basic arithmetic operations include addition, subtraction, multiplication and division.

### **Binary addition:**

There are four rules for binary addition:

| Input A | Input B | Sum (S)<br>A+B | Carry (C) |

|---------|---------|----------------|-----------|

| О       | О       | О              | 0         |

| О       | 1       | 1              | 0         |

| 1       | 0       | 1              | 0         |

| 1       | 1       | 0              | 1         |

### Example-

### **Binary subtraction:**

There are four rules for binary subtraction:

| Input A | Input B | Subtract<br>(S)<br>A-B | Borrow (B) |

|---------|---------|------------------------|------------|

| О       | О       | 0                      | О          |

| О       | 1       | О                      | 1          |

| 1       | 0       | 1                      | О          |

| 1       | 1       | 0                      | О          |

### Example-

### **Binary multiplication:**

There are four rules of binary multiplication.

| Input A | Input B | Multiply<br>(M)<br>AxB |

|---------|---------|------------------------|

| 0       | О       | 0                      |

| 0       | 1       | 0                      |

| 1       | 0       | 0                      |

| 1       | 1       | 1                      |

#### Example:

0011010 × 001100 = 100111000

### **Binary division:**

There are four parts in any division: Dividend, Divisor, quotient, and remainder.

| Input A | Input B | Divide (D)<br>A/B |

|---------|---------|-------------------|

| О       | 0       | Not defined       |

| 0       | 1       | 0                 |

| 1       | 0       | Not defined       |

| 1       | 1       | 1                 |

### Example-

101010 / 000110 = 000111

$$\begin{array}{r}

111 & = 710 \\

000110 ) -101010 & = 4210 \\

-110 & = 610 \\

\hline

& 001 \\

-110 & = 110 \\

\hline

& 001 \\

-110 & = 0

\end{array}$$

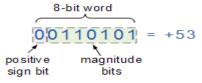

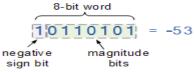

### Signed binary number representation:

- In mathematics, positive numbers (including zero) are represented as unsigned numbers.

- That is, we do not put the +ve sign in front of them to show that they are positive numbers.

- However, when dealing with negative numbers we do use a -ve sign in front of the number to show that the number is negative in value and different from a positive unsigned value, and the same is true with signed binary numbers.

- However, in digital circuits there is no provision made to put a plus or even a minus sign to a number, since digital systems operate with binary numbers that are represented in terms of "0's" and "1's".

- For signed binary numbers the most significant bit (MSB) is used as the sign bit.

- If the sign bit is "0", this means the number is positive in value.

- If the sign bit is "1", then the number is negative in value.

3 ways to represent negative binary number-

- 1. Sign magnitude

- 2. 1's compliment

### 3. 2' compliment Sign magnitude:

Left most digit is used to indicate the sign and the remaining digits the magnitude or value of the number.

### Example-

### Positive sign magnitude:

### **Negative sign magnitude:**

The disadvantage here is that whereas before we had a full range n-bit unsigned binary number, we now have an n-1 bit signed binary number giving a reduced range of digits from:

$$-2(n-1)$$

to  $+2(n-1)$

### 1's complement:

- The one's complement of a negative binary number is the complement of its positive counterpart.

- Thus, the one's complement of "1" is "0" and vice versa, then the one's complement of 100101002 is simply 011010112 as all the 1's are changed to 0's and the 0's to 1's. □ For representing the positive numbers, there is nothing to do.

But for representing negative numbers, we have to use 1's complement technique.

• For representing the negative number, we first have to represent it with a positive sign, and then we find the 1's complement of it.

Example- 11010.1101

For finding 1's complement of the given number, change all 0's to 1 and all 1's to 0. So, the 1's complement of the number 11010.1101 comes out 00101.0010. **2's complement:**

- 2's complement is also used to represent the signed binary numbers.

- For finding 2's complement of the binary number, we will first find the 1's complement of the binary number and then add 1 to the least significant bit of it.

Example- 110100

For finding 2's complement of the given number, change all 0's to 1 and all 1's to 0. So, the 1's complement of the number 110100 is 001011. Now add 1 to the LSB of this number, i.e., (001011)+1=001100.

### Addition and subtraction using 1's complement:

There are three different cases possible when we add two binary numbers which are as follows:

### Case 1: Addition of the positive number with a negative number when the positive number has a greater magnitude.

Initially, calculate the 1's complement of the given negative number. Sum up with the given positive number. If we get the end-around carry 1, it gets added to the LSB.

Example: 1101 and -1001

- First, find the 1's complement of the negative number 1001. So, for finding 1's complement, change all 0 to 1 and all 1 to 0. The 1's complement of the number 1001 is 0110.

- Now, add both the numbers, i.e., 1101 and 0110; 1101+0110=1 0011

- By adding both numbers, we get the end-around carry 1. We add this end around carry to the LSB of 0011. 0011+1=0100

### Case 2: Adding a positive value with a negative value in case the negative number has a higher magnitude.

Initially, calculate the 1's complement of the negative value. Sum it with a positive number. In this case, we did not get the end-around carry. So, take the 1's complement of the result to get the final result.

Note: The resultant is a negative value.

Example: 1101 and -1110

- First find the 1's complement of the negative number 1110. So, for finding 1's complement, we change all 0 to 1, and all 1 to 0. 1's complement of the number 1110 is 0001.

- Now, add both the numbers, i.e., 1101 and 0001; 1101+0001= 1110

- Now, find the 1's complement of the result 1110 that is the final result. So, the 1's complement of the result 1110 is 0001, and we add a negative sign before the number so that we can identify that it is a negative number.

### **Case 3: Addition of two negative numbers**

In this case, first find the 1's complement of both the negative numbers, and then we add both these complement numbers. In this case, we always get the end-around carry, which get added to the LSB, and for getting the final result, we take the 1's complement of the result.

Note: The resultant is a negative value.

Example: -1101 and -1110 in five-bit register

- Firstly, find the 1's complement of the negative numbers 01101 and 01110. So, for finding 1's complement, we change all 0 to 1, and all 1 to 0. 1's complement of the number 01110 is 10001, and 01101 is 10010.

- Now, we add both the complement numbers, i.e., 10001 and 10010; 10001+10010= 1 00011

- By adding both numbers, we get the end-around carry 1. We add this end-around carry to the LSB of 00011. 00011+1=00100

- Now, find the 1's complement of the result 00100 that is the final answer. So, the 1's

complement of the result 00100 is 110111, and add a negative sign before the number

so that we can identify that it is a negative number.

### Addition and subtraction using 2's complement:

There are three different cases possible when we add two binary numbers using 2's complement, which is as follows:

### Case 1: Addition of the positive number with a negative number when the positive number has a greater magnitude.

Initially find the 2's complement of the given negative number. Sum up with the given positive number. If we get the end-around carry 1 then the number will be a positive number and the carry bit will be discarded and remaining bits are the final result.

Example: 1101 and -1001

- First, find the 2's complement of the negative number 1001. So, for finding 2's complement, change all 0 to 1 and all 1 to 0 or find the 1's complement of the number 1001. The 1's complement of the number 1001 is 0110, and add 1 to the LSB of the result 0110. So the 2's complement of number 1001 is 0110+1=0111

- Add both the numbers, i.e., 1101 and 0111; 1101+0111=1 0100

- By adding both numbers, we get the end-around carry 1. We discard the end-around carry. So, the addition of both numbers is 0100.

### Case 2: Adding of the positive value with a negative value when the negative number has a higher magnitude.

Initially, add a positive value with the 2's complement value of the negative number. Here, no end-around carry is found. So, we take the 2's complement of the result to get the final result. Note: The resultant is a negative value.

Example: 1101 and -1110

- First, find the 2's complement of the negative number 1110. So, for finding 2's complement, add 1 to the LSB of its 1's complement value 0001.

0001+1=0010

- Add both the numbers, i.e., 1101 and 0010;

1101+0010= 1111

- Find the 2's complement of the result 1110 that is the final result. So, the 2's complement of the result 1110 is 0001, and add a negative sign before the number so that we can identify that it is a negative number.

### Case 3: Addition of two negative numbers

In this case, first, find the 2's complement of both the negative numbers, and then we will add both these complement numbers. In this case, we will always get the end-around carry, which will be added to the LSB, and forgetting the final result, we will take the 2's complement of the result.

Note: The resultant is a negative value.

Example: -1101 and -1110 in five-bit register

• Firstly, find the 2's complement of the negative numbers 01101 and 01110. So, for finding 2's complement, we add 1 to the LSB of the 1's complement of these numbers. 2's complement of the number 01110 is 10010, and 01101 is 10011.

• We add both the complement numbers, i.e., 10001 and 10010:

10010+10011= 1 00101

By adding both numbers, we get the end-around carry 1. This carry is discarded and the final result is the 2.s complement of the result 00101. So, the 2's complement of the result 00101 is 11011, and we add a negative sign before the number so that we can identify that it is a negative number.

### Digital codes:

In the coding, when numbers or letters are represented by a specific group of symbols, it is said to be that number or letter is being encoded. The group of symbols is called as code. The digital data is represented, stored and transmitted as group of bits. This group of bits is also called as binary code.

### **Advantages of Binary Code:**

- Binary codes are suitable for the computer applications.

- Binary codes are suitable for the digital communications.

- Binary codes make the analysis and designing of digital circuits if we use the binary codes.

- Since only 0 & 1 are being used, implementation becomes easy. Classification of binary codes:

The codes are broadly categorized into following four categories.

- Weighted Codes

- Non-Weighted Codes

- · Binary Coded Decimal Code

- Alphanumeric Codes

- Error Detecting Codes

- Error Correcting Codes Weighted Codes:

Weighted binary codes are those binary codes which obey the positional weight principle. Each position of the number represents a specific weight. Several systems of the codes are used to express the decimal digits 0 through 9. In these codes each decimal digit is represented by a group of four bits.

| Decimal Digit | 8421 Code | 2421 Code | 84-2-1 Code |

|---------------|-----------|-----------|-------------|

| 0             | 0000      | 0000      | 0000        |

| 1             | 0001      | 0001      | 0111        |

| 2             | 0010      | 0010      | 0110        |

| 3             | 0011      | 0011      | 0101        |

| 4             | 0100      | 0100      | 0100        |

| 5 | 0101 | 1011 | 1011 |

|---|------|------|------|

| 6 | 0110 | 1100 | 1010 |

| 7 | 0111 | 1101 | 1001 |

| 8 | 1000 | 1110 | 1000 |

| 9 | 1001 | 1111 | 1111 |

### 8 4 2 1 code

- The weights of this code are 8, 4, 2 and 1.

- This code has all positive weights. So, it is a **positively weighted code**.

- This code is also called as **natural BCDBinary Coded Decimalcode**.

- In this code each decimal digit is represented by a 4-bit binary number.

- BCD is a way to express each of the decimal digits with a binary code.

- In the BCD, with four bits we can represent sixteen numbers (0000 to 1111).

- But in BCD code only first ten of these are used (0000 to 1001).

- The remaining six code combinations i.e., 1010 to 1111 are invalid in BCD.

| Decimal | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---------|------|------|------|------|------|------|------|------|------|------|

| BCD     | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 |

### Example

Let us find the BCD equivalent of the decimal number 786. This number has 3 decimal digits 7, 8 and 6. From the table, we can write the BCD 84218421 codes of 7, 8 and 6 are 0111, 1000 and 0110 respectively.

$786_{10} = 0111\ 1000\ 0110_{BCD}$

There are 12 bits in BCD representation, since each BCD code of decimal digit has 4 bits.

### **Advantages of BCD Codes**

- It is very similar to decimal system.

- We need to remember binary equivalent of decimal numbers 0 to 9 only.

### **Disadvantages of BCD Codes**

- The addition and subtraction of BCD have different rules.

- The BCD arithmetic is little more complicated.

- BCD needs more number of bits than binary to represent the decimal number. So, BCD is less efficient than binary.

**Non-weighted code:** n this type of binary codes, the positional weights are not assigned. The examples of

nonweighted codes are Excess-3 code and Gray code.

### Excess-3 code

- The Excess-3 code is also called as XS-3 code.

- It is non-weighted code used to express decimal numbers.

The Excess-3 code words are derived from the 8421 BCD code words adding (0011)2 or (3)10 to each code word in 8421.

- The excess-3 codes are obtained as follows –

| Decimal BCD 8 4 2 1 | Excess-3 |            |

|---------------------|----------|------------|

|                     | 8 4 2 1  | BCD + 0011 |

| 0                   | 0 0 0 0  | 0 0 1 1    |

| 1                   | 0 0 0 1  | 0 1 0 0    |

| 2                   | 0 0 1 0  | 0 1 0 1    |

| 3                   | 0 0 1 1  | 0 1 1 0    |

| 4                   | 0 1 0 0  | 0 1 1 1    |

| 5                   | 0 1 0 1  | 1 0 0 0    |

| 6                   | 0 1 1 0  | 1 0 0 1    |

| 7                   | 0 1 1 1  | 1 0 1 0    |

| 8                   | 1 0 0 0  | 1 0 1 1    |

| 9                   | 1 0 0 1  | 1 1 0 0    |

### **Gray Code**

- It is the non-weighted code and it is not arithmetic codes.

- That means there are no specific weights assigned to the bit position.

- It has a very special feature that, only one bit will change each time the decimal number is incremented as shown in fig.

- As only one-bit changes at a time, the gray code is called as a unit distance code.

- The gray code is a cyclic code. Gray code cannot be used for arithmetic operation.

| Decimal | BCD     | Gray    |

|---------|---------|---------|

| 0       | 0 0 0 0 | 0 0 0 0 |

| 1       | 0 0 0 1 | 0 0 0 1 |

| 2       | 0 0 1 0 | 0 0 1 1 |

| 3       | 0 0 1 1 | 0 0 1 0 |

| 4       | 0 1 0 0 | 0 1 1 0 |

| 5       | 0 1 0 1 | 0 1 1 1 |

| 6       | 0 1 1 0 | 0 1 0 1 |

| 7       | 0 1 1 1 | 0 1 0 0 |

| 8       | 1 0 0 0 | 1 1 0 0 |

| 9       | 1 0 0 1 | 1 1 0 1 |

### **Binary code to Gray Code Conversion:**

• Consider the given binary code and place the MSB of binary to the left of MSB.

Compare the successive two bits starting from MSB. If the 2 bits are same, then the output is zero. Otherwise, output is one.

Repeat the above step till the LSB of Gray code is obtained.

### Example-

From the table, we know that the Gray code corresponding to binary code 1000 is 1100. Now, let us verify it by using the above procedure. Given, binary code is 1000. Step 1 – By placing same MSB to the left of MSB, the binary code will be 1000.

Step 2 – By comparing successive two bits of new binary code, we will get the gray code as 1100.

### **Application of Gray code:**

- Gray code is popularly used in the shaft position encoders.

- A shaft position encoder produces a code word which represents the angular position of the shaft.

### Alphanumeric codes:

- A binary digit or bit can represent only two symbols as it has only two states '0' or '1'.

- But this is not enough for communication between two computers because there we need many more symbols for communication.

- These symbols are required to represent 26 alphabets with capital and small letters, numbers from 0 to 9, punctuation marks and other symbols.

- The alphanumeric codes are the codes that represent numbers and alphabetic characters.

- Mostly such codes also represent other characters such as symbol and various instructions necessary for conveying information.

- An alphanumeric code should at least represent 10 digits and 26 letters of alphabet i.e. total 36 items.

- The following two alphanumeric codes are very commonly used for the data representation.

- i. American Standard Code for Information Interchange (ASCII).

- ii. Extended Binary Coded Decimal Interchange Code (EBCDIC).

- ASCII code is a 7-bit code whereas EBCDIC is an 8-bit code.

- ASCII code is more commonly used worldwide while EBCDIC is used primarily in large IBM computers.

### **Error detection codes:**

- Error detection codes are used to detect the errors present in the received data bitstream.

- These codes contain some bits, which are included appended to the original bit stream

- These codes detect the error, if it is occurred during transmission of the original data bitstream.

- Example Parity code, Hamming code.

### Error correction codes:

- Error correction codes are used to correct the errors present in the received data bitstream so that, we will get the original data.

- Error correction codes also use the similar strategy of error detection codes.

- Example Hamming code.

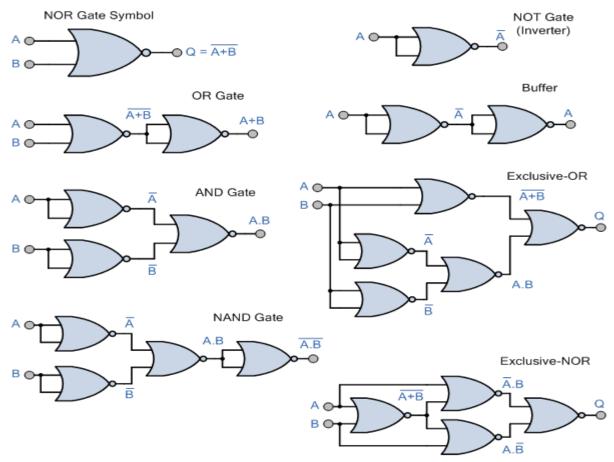

Therefore, to detect and correct the errors, additional bits are appended to the data bits at the time of transmission. **Logic gates:**

- Logic gates play an important role in circuit design and digital systems.

- It is a building block of a digital system and an electronic circuit that always have only one output.

These gates can have one input or more than one input, but most of the gates have two inputs.

We can classify these Logic gates into the following three categories.

- 1. Basic gates

- 2. Universal gates

- 3. Special gates Basic gates:

The basic gates are AND, OR & NOT gates.

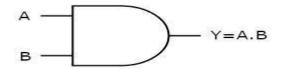

### AND gate:

An AND gate is a digital circuit that has two or more inputs and produces an output, which is the **logical AND** of all those inputs. It is optional to represent the **Logical AND** with the symbol ','

The following table shows the **truth table** of 2-input AND gate.

| Α | В | Y = A.B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 0       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

Here A, B are the inputs and Y is the output of two input AND gate. If both inputs are '1', then only the output, Y is '1'. For remaining combinations of inputs, the output, Y is '0'.

The following figure shows the **symbol** of an AND gate, which is having two inputs A, B and one output, Y.

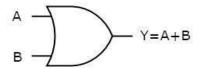

### OR gate:

An OR gate is a digital circuit that has two or more inputs and produces an output, which is the logical OR of all those inputs. This **logical OR** is represented with the symbol '+'. The following table shows the **truth table** of 2-input OR gate.

| Α | В | Y = A + B |

|---|---|-----------|

| 0 | 0 | 0         |

| 0 | 1 | 1 |

|---|---|---|

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Here A, B are the inputs and Y is the output of two input OR gate. If both inputs are '0', then only the output, Y is '0'. For remaining combinations of inputs, the output, Y is '1'.

The following figure shows the **symbol** of an OR gate, which is having two inputs A, B and one output, Y.

This OR gate produces an output Y, which is the logical OR of two inputs A, B.

### NOT gate:

A NOT gate is a digital circuit that has single input and single output. The output of NOT gate is the **logical inversion** of input. Hence, the NOT gate is also called as inverter. The following table shows the **truth table** of NOT gate.

| Α | Y = A' |

|---|--------|

| 0 | 1      |

| 1 | 0      |

Here A and Y are the input and output of NOT gate respectively. If the input, A is '0', then the output, Y is '1'. Similarly, if the input, A is '1', then the output, Y is '0'.

The following figure shows the **symbol** of NOT gate, which is having one input, A and one output, Y.

This NOT gate produces an output Y, which is the **complement** of input, A.

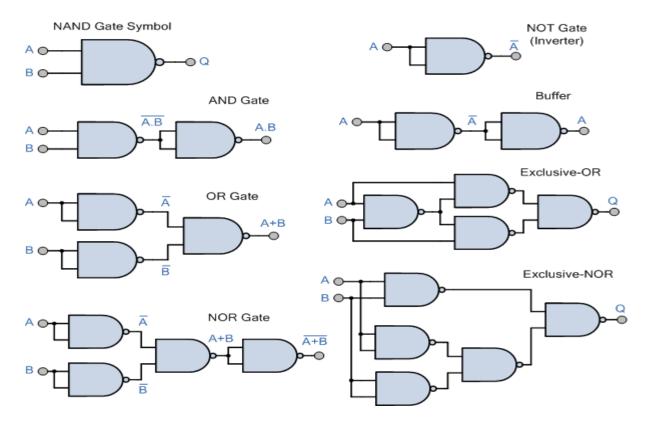

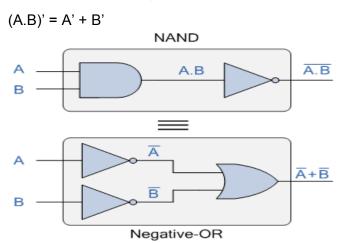

### Universal gates

NAND & NOR gates are called as universal gates.

### NAND gate

NAND gate is a digital circuit that has two or more inputs and produces an output, which is the **inversion of logical AND** of all those inputs.

The following table shows the **truth table** of 2-input NAND gate.

| Α | В | <b>Y = (</b> A.B)' |

|---|---|--------------------|

|   |   |                    |

0

0

1

1

1

0

1

1

0

0

The following image shows the **symbol** of NAND gate, which is having two inputs A, B and one output, Y.

NAND gate operation is same as that of AND gate followed by an inverter. That's why the NAND gate symbol is represented like that.

### NOR gate:

NOR gate is a digital circuit that has two or more inputs and produces an output, which is the **inversion of logical OR** of all those inputs.

The following table shows the truth table of 2-input NOR gate

| Α | В | <b>Y = (</b> A+B)' |

|---|---|--------------------|

| 0 | 0 | 1                  |

| 0 | 1 | 0                  |

| 1 | 0 | 0                  |

| 1 | 1 | 0                  |

The following figure shows the **symbol** of NOR gate, which is having two inputs A, B and one output, Y.

NOR gate operation is same as that of OR gate followed by an inverter. That's why the NOR gate symbol is represented like that.

### **Special Gates**

Ex-OR & Ex-NOR gates are called as special gates. Because, these two gates are special cases of OR & NOR gates.

### Ex-OR gate:

The full form of Ex-OR gate is **Exclusive-OR** gate. Its function is same as that of OR gate except for some cases, when the inputs having even number of ones. The following table shows the **truth table** of 2-input Ex-OR gate.

| A | В | Y = A⊕B |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

The output of Ex-OR gate is '1', when only one of the two inputs is '1'. And it is zero, when both inputs are same.

Below figure shows the **symbol** of Ex-OR gate, which is having two inputs A, B and one output, Y.

The output of Ex-OR gate is '1', when odd number of ones present at the inputs. Hence, the output of Ex-OR gate is also called as an **odd function**.

### Ex-NOR gate:

The full form of Ex-NOR gate is **Exclusive-NOR** gate. Its function is same as that of NOR gate except for some cases, when the inputs having even number of ones. The following table shows the **truth table** of 2-input Ex-NOR gate.

| A | В | Y = A⊙B |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 0       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

The output of Ex-NOR gate is '1', when both inputs are same. And it is zero, when both the inputs are different.

The following figure shows the **symbol** of Ex-NOR gate, which is having two inputs A, B and one output, Y.

The output of Ex-NOR gate is '1', when even number of ones present at the inputs. Hence, the output of Ex-NOR gate is also called as an **even function**.

From the above truth tables of Ex-OR & Ex-NOR logic gates, we can easily notice that the ExNOR operation is just the logical inversion of Ex-OR operation.

### Universal gates and its realization:

We can realise all of the other gates by using just one single type of universal logic gate, the NAND (NOT AND) or the NOR (NOT OR) gate, thereby reducing the number of different types of logic gates required, and also the cost. Thus, the NAND and the NOR gates are commonly referred to as Universal Logic Gates. **Implementation of logic gates using NAND gate only:**

### Implementation of logic gates using NOR gate only:

### **Boolean Algebra:**

Boolean Algebra is used to analyse and simplify the digital (logic) circuits. It uses only the binary numbers i.e., 0 and 1. It is also called as Binary Algebra or logical Algebra. Boolean algebra was invented by George Boole in 1854.

### **Boolean Laws**

There are six types of Boolean Laws.

### **Commutative law**

Any binary operation which satisfies the following expression is referred to as commutative operation.

(i)

$$A.B = B.A$$

(ii)  $A + B = B + A$

Commutative law states that changing the sequence of the variables does not have any effect on the output of a logic circuit.

### Associative law

This law states that the order in which the logic operations are performed is irrelevant as their effect is the same.

(i)

$$(A.B).C = A.(B.C)$$

(ii)

$$(A + B) + C = A + (B + C)$$

### Distributive law

Distributive law states the following condition.

$$A.(B+C) = A.B + A.C$$

### **AND law**

These laws use the AND operation. Therefore, they are called as **AND** laws.

(i)

$$A.0 = 0$$

(ii)

$$A.1 = A$$

(iv)

$$A.\overline{A} = 0$$

### **OR law**

These laws use the OR operation. Therefore, they are called as OR laws.

(i)

$$A + 0 = A$$

(ii)

$$A + 1 = 1$$

(iv)

$$A + \overline{A} = 1$$

#### **INVERSION law**

This law uses the NOT operation. The inversion law states that double inversion of a variable results in the original variable itself.

$$\frac{=}{A} = A$$

### **Boolean Function:**

Boolean algebra deals with binary variables and logic operation. A **Boolean Function** is described by an algebraic expression called **Boolean expression** which consists of binary variables, the constants 0 and 1, and the logic operation symbols. Consider the following example.

Equation No. 1

**Boolean Function**

**Boolean Expression**

Here the left side of the equation represents the output Y. So we can state equation no. 1

$$Y = A + BC + ADC$$

### **Truth Table Formation**

A truth table represents a table having all combinations of inputs and their corresponding result.

It is possible to convert the switching equation into a truth table. For example, consider the following switching equation.

The output will be high (1) if A = 1 or BC = 1 or both are 1. The truth table for this equation is shown by Table (a). The number of rows in the truth table is  $2^n$  where n is the number of input variables (n=3 for the given equation). Hence there are  $2^3 = 8$  possible input combination of inputs.

| Inputs |   | 5 | Output |

|--------|---|---|--------|

| Α      | В | С | F      |

| 0      | 0 | 0 | 0      |

| 0      | 0 | 1 | 0      |

| 0      | 1 | 0 | 0      |

| 0      | 1 | 1 | 1      |

| 1      | 0 | 0 | 1      |

| 1      | 0 | 1 | 1      |

| 1      | 1 | 0 | 1      |

| 1      | 1 | 1 | 1      |

### **De Morgan's Theorem:**

**De Morgan's 1**<sup>st</sup> **theorem** states that the complement of the product of all the terms is equal to the sum of the complement of each term.

**De Morgan's 2**<sup>nd</sup> **theorem** states that the complement of the sum of all the terms is equal to the product of the complement of each term.

### **Duality Theorem:**

This theorem states that the dual of the Boolean function is obtained by interchanging the logical AND operator with logical OR operator and zeros with ones. For every Boolean function, there will be a corresponding Dual function.

| Group1        | Group2    |

|---------------|-----------|

| x + 0 = x     | x.1 = x   |

| x + 1 = 1     | x.0 = 0   |

| X + X = X     | x.x = x   |

| x + x' = 1    | x.x' = 0  |

| x + y = y + x | x.y = y.x |

### Example-1:

Given Boolean function, f = p'qr + pq'r + pqr' + pqr.

**Step 1** – Use the **Boolean postulate**, x + x = x. That means, the Logical OR operation with any Boolean variable 'n' times will be equal to the same variable. So, we can write the last term pqr two more times.

$$\Rightarrow$$

f = p'qr + pq'r + pqr + pqr + pqr

**Step 2** – Use **Distributive law** for 1<sup>st</sup> and 4<sup>th</sup> terms, 2<sup>nd</sup> and 5<sup>th</sup> terms, 3<sup>rd</sup> and 6<sup>th</sup> terms.

$$\Rightarrow$$

f = qrp'+pp'+p + prq'+qq'+q + pqr'+rr'+r

**Step 3** – Use **Boolean postulate**, x + x' = 1 for simplifying the terms present in each parenthesis.

$$\Rightarrow$$

f = qr11 + pr11 + pq11

**Step 4** – Use **Boolean postulate**, x.1 = x for simplifying the above three terms.

$$\Rightarrow$$

f = qr + pr + pq $\Rightarrow$  f =

pq + qr + pr Therefore, the simplified Boolean function is f = pq

+ qr + pr.

### Example-2:

Let us find the complement of the Boolean function, f = p'q + pq'. The complement of Boolean function is f' = p'q + pq'p'q + pq''.

**Step 1** – Use DeMorgan's theorem,  $x+yx+y' = x'.y'. \Rightarrow f'$

$$= p'qp'q'.pq'pq''$$

Step 2 – Use DeMorgan's theorem, x.yx.y' = x' + y'

$$\Rightarrow f' = \{p'p'' + q'\}.\{p' + q'q''\}$$

**Step3** – Use the Boolean postulate,

$$x'x''=x$$

.  $\Rightarrow f' = \{p + p\}$

$$q'$$

.{ $p' + q$ }  $\Rightarrow$   $f' = pp' + pq + p'q' + qq'$

Step 4 - Use the Boolean postulate, xx'=0.

$$\Rightarrow f = 0 + pq + p'q' + 0 \Rightarrow$$

$$f = pq + p'q'$$

Therefore, the **complement** of Boolean function, p'q + pq' is pq + p'q'.

### **SOP and POS form:**

### **Sum of Product (SOP):**

- The Sum of Product expression is equivalent to the logical AND function which Sums two or more Products to produce an output.

- We will get four Boolean product terms by combining two variables x and y with logical AND operation.

- These Boolean product terms are called as min terms or standard product terms.

- If the binary variable is '0', then it is represented as complement of variable and '1' as normal form in min term. The min terms are x'y', x'y, xy' and xy. **Product of Sum (POS):**

- The Product of Sum expression is equivalent to the logical OR-AND function which gives the AND Product of two or more OR Sums to produce an output.

- We will get four Boolean sum terms by combining two variables x and y with logical OR operation.

- These Boolean sum terms are called as **Max terms** or **standard sum terms**. ☐ If the binary variable is '1', then it is represented as complement of variable and '0' as normal form in Max term. The Max terms are x + y, x + y', x' + y and x' + y'.

| x | у | Min terms            | Max terms               |

|---|---|----------------------|-------------------------|

| 0 | 0 | m <sub>0</sub> =x'y' | $M_0=x+y$               |

| 0 | 1 | m₁=x'y               | M <sub>1</sub> =x + y'  |

| 1 | 0 | m <sub>2</sub> =xy'  | M <sub>2</sub> =x' + y  |

| 1 | 1 | m <sub>3</sub> =xy   | M <sub>3</sub> =x' + y' |

### **Canonical SOP and POS forms:**

- A truth table consists of a set of inputs and outputs.

- If there are 'n' input variables, then there will be 2<sup>n</sup> possible combinations with zeros and ones.

- So, the value of each output variable depends on the combination of input variables.

- So, each output variable will have '1' for some combination of input variables and '0' for some other combination of input variables.

Therefore, we can express each output variable in following two ways.

- Canonical SOP form

- Canonical POS form Canonical SOP form:

- Canonical SOP form means Canonical Sum of Products form.

- In this form, each product term contains all literals.

- So, these product terms are nothing but the min terms. Hence, canonical SOP form is also called as **sum of min terms** form.

- First, identify the min terms for which, the output variable is one and then do the logical OR of those min terms in order to get the Boolean expression function corresponding to that output variable. This Boolean function will be in the form of sum of min terms.

- Follow the same procedure for other output variables also, if there is more than one output variable. **Example**

Consider the following truth table.

| Inputs |   | Ou:put |   |

|--------|---|--------|---|

| р      | Q | r      | f |

| 0      | 0 | 0      | 0 |

| 0      | 0 | 1      | 0 |

| 0      | 1 | 0      | 0 |

| 0      | 1 | 1      | 1 |

| 1      | 0 | 0      | 0 |

| 1      | 0 | 1      | 1 |

| 1      | 1 | 0      | 1 |

| 1      | 1 | 1      | 1 |

- Here, the output f is '1' for four combinations of inputs.

- The corresponding min terms are p'qr, pq'r, pqr', pqr.

- By doing logical OR of these four min terms, we will get the Boolean function of output f.

Therefore, the Boolean function of output is, f = p'qr + pq'r + pqr' + pqr.

This is the **canonical SOP form** of output, f. We can also represent this function in following two notations.

$$f = m3+m5+m6+m7 f = \sum m(3,5,6,7)$$

In one equation, we represented the function as sum of respective min terms. In other equation, we used the symbol for summation of those min terms. **Canonical POS form:**

- Canonical POS form means Canonical Product of Sums form.

- In this form, each sum term contains all literals. So, these sum terms are nothing but the Max terms. Hence, canonical POS form is also called as product of Max terms form.

- First, identify the Max terms for which, the output variable is zero and then do the logical AND of those Max terms in order to get the Boolean expression function corresponding to that output variable. This Boolean function will be in the form of product of Max terms.

- Follow the same procedure for other output variables also, if there is more than one output variable.

### Example

- Consider the same truth table of previous example.

Here, the output f is '0' for four combinations of inputs.

The corresponding Max terms are p + q + r, p + q + r, p + q + r, p' + q + r.

- By doing logical AND of these four Max terms, we will get the Boolean function of output f.

Therefore, the Boolean function of output is, f =

(p+q+r). (p+q+r'). (p+q'+r). (p'+q+r).

This is the **canonical POS form** of output, f.

We can also represent this function in following two notations. f=M0.M1.M2.M4  $f=\prod M(0,1,2,4)$  In one equation, we represented the function as product of respective Max terms. In other equation, we used the symbol for multiplication of those Max terms. The Boolean function,

f = (p+q+r). (p+q+r'). (p+q'+r). (p'+q+r)

is the dual of the Boolean function, f

= p'qr + pq'r + pqr' + pqr.

Therefore, both canonical SOP and canonical POS forms are **Dual** to each other. Functionally, these two forms are same. Based on the requirement, we can use one of these two forms.

### Standard SOP and POS forms

We discussed two canonical forms of representing the Boolean outputs. Similarly, there are two standard forms of representing the Boolean outputs. These are the simplified version of canonical forms.

- Standard SOP form

- Standard POS form

The main **advantage** of standard forms is that the number of inputs applied to logic gates can be minimized. Sometimes, there will be reduction in the total number of logic gates required.

### **Standard SOP form:**

Standard SOP form means **Standard Sum of Products** form. In this form, each product term need not contain all literals. So, the product terms may or may not be the min terms.

Therefore, the Standard SOP form is the simplified form of canonical SOP form.

We will get Standard SOP form of output variable in two steps.

- Get the canonical SOP form of output variable

- Simplify the above Boolean function, which is in canonical SOP form.

Follow the same procedure for other output variables also, if there is more than one output variable. Sometimes, it may not possible to simplify the canonical SOP form. In that case, both canonical and standard SOP forms are same.

### Example

Convert the following Boolean function into Standard SOP form. f

$$= p'qr + pq'r + pqr' + pqr$$

The given Boolean function is in canonical SOP form. Now, we have to simplify this Boolean function in order to get standard SOP form.

**Step 1** – Use the **Boolean postulate**, x + x = x. That means, the Logical OR operation with any Boolean variable 'n' times will be equal to the same variable. So, we can write the last term pqr two more times.

$$\Rightarrow$$

f = p'qr + pq'r + pqr' + pqr + pqr + pqr

Step 2 - Use Distributive law for 1<sup>st</sup> and 4<sup>th</sup> terms, 2<sup>nd</sup> and 5<sup>th</sup> terms, 3<sup>rd</sup> and 6<sup>th</sup> terms. ⇒

$$f = qr(p'+p) + pr(q'+q) + pq(r'+r)$$

**Step 3** – Use **Boolean postulate**, x + x' = 1 for simplifying the terms present in each parenthesis.  $\Rightarrow$  f = qr 1 + pr 1 + pq 1

**Step 4** – Use **Boolean postulate**, x.1 = x for simplifying above three terms.

$$\Rightarrow f = qr + pr + pq \Rightarrow$$

$$f = pq + qr + pr$$

This is the simplified Boolean function. Therefore, the **standardSOP form** corresponding to given canonical SOP form is f = pq + qr + prStandard POS form:

Standard POS form means **Standard Product of Sums** form. In this form, each sum term need not contain all literals. So, the sum terms may or may not be the Max terms. Therefore, the Standard POS form is the simplified form of canonical POS form.

We will get Standard POS form of output variable in two steps.

- Get the canonical POS form of output variable

- Simplify the above Boolean function, which is in canonical POS form.

Follow the same procedure for other output variables also, if there is more than one output variable. Sometimes, it may not possible to simplify the canonical POS form. In that case, both canonical and standard POS forms are same.

#### Example

Convert the following Boolean function into Standard POS form.

$$f = (p+q+r). (p+q+r'). (p+q'+r). (p'+q+r)$$

The given Boolean function is in canonical POS form. Now, we have to simplify this Boolean function in order to get standard POS form.

**Step 1** – Use the **Boolean postulate**, x.x = x. That means, the Logical AND operation with any Boolean variable 'n' times will be equal to the same variable. So, we can write the first term p+q+r two more times.

$$\Rightarrow$$

f = (p+q+r). (p+q+r). (p+q+r). (p+q+r'). (p+q'+r). (p'+q+r)

**Step 2** – Use **Distributive law**, x + y.z = (x+y). (x+z) for 1<sup>st</sup> and 4<sup>th</sup> parenthesis, 2<sup>nd</sup> and 5<sup>th</sup> parenthesis, 3<sup>rd</sup> and 6<sup>th</sup> parenthesis.

$$\Rightarrow$$

f = (p+q+rr'). (p+r+qq'). (q+r+pp')

**Step 3** – Use **Boolean postulate**, x.x'=0 for simplifying the terms present in each parenthesis.  $\Rightarrow$  f = (p+q+0). (p+r+0). (q+r+0)

**Step 4** – Use **Boolean postulate**, x + 0 = x for simplifying the terms present in each parenthesis  $\Rightarrow$  f = (p+q). (q+r). (q+r)  $\Rightarrow$  f = (p+q). (q+r). (p+r)

This is the simplified Boolean function. Therefore, the **standard POS form** corresponding to given canonical POS form is f = (p+q). (q+r). (p+r). This is the **dual** of the Boolean function, f = pq + qr + pr.

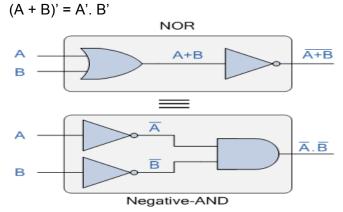

Therefore, both Standard SOP and Standard POS forms are Dual to each other. **Karnaugh map:**

• Karnaugh introduced a method for simplification of Boolean functions in an easy way. This method is known as Karnaugh map method or K-map method.

• It is a graphical method, which consists of 2n cells for 'n' variables.

The adjacent cells are differed only in single bit position.

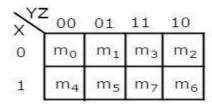

#### 2-Variable K-Map:

The number of cells in 2 variable K-map is four, since the number of variables is two.

- There is only one possibility of grouping 4 adjacent min terms.

- The possible combinations of grouping 2 adjacent min terms are  $\{(m_0, m_1), (m_2, m_3), (m_0, m_2) \text{ and } (m_1, m_3)\}$ . **3-Variable K-Map:**

The number of cells in 3 variable K-map is eight, since the number of variables is three.

- There is only one possibility of grouping 8 adjacent min terms.

- The possible combinations of grouping 4 adjacent min terms are  $\{(m_0, m_1, m_3, m_2), (m_4, m_5, m_7, m_6), (m_0, m_1, m_4, m_5), (m_1, m_3, m_5, m_7), (m_3, m_2, m_7, m_6) \text{ and } (m_2, m_0, m_6, m_4)\}.$

- The possible combinations of grouping 2 adjacent min terms are  $\{(m_0, m_1), (m_1, m_3), (m_3, m_2), (m_2, m_0), (m_4, m_5), (m_5, m_7), (m_7, m_6), (m_6, m_4), (m_0, m_4), (m_1, m_5), (m_3, m_7)$ and  $\{(m_2, m_6)\}$ .

- If x=0, then 3 variable K-map becomes 2 variable K-map.

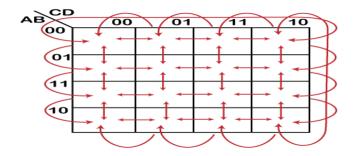

# 4-Variable K-Map:

The number of cells in 4 variable K-map is sixteen, since the number of variables is four.

| wx YZ | 00              | 01              | 11              | 10              |

|-------|-----------------|-----------------|-----------------|-----------------|

| 00    | m <sub>0</sub>  | m <sub>1</sub>  | m <sub>3</sub>  | m <sub>2</sub>  |

| 01    | m <sub>4</sub>  | m <sub>5</sub>  | m <sub>7</sub>  | m <sub>6</sub>  |

| 11    | m <sub>12</sub> | m <sub>13</sub> | m <sub>15</sub> | m <sub>14</sub> |

| 10    | m <sub>8</sub>  | m <sub>9</sub>  | m <sub>11</sub> | m <sub>10</sub> |

• There is only one possibility of grouping 16 adjacent min terms.

- Let R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> and R<sub>4</sub> represents the min terms of first row, second row, third row and fourth row respectively. Similarly, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> and C<sub>4</sub> represents the min terms of first column, second column, third column and fourth column respectively. The possible combinations of grouping 8 adjacent min terms are {(R<sub>1</sub>, R<sub>2</sub>), (R<sub>2</sub>, R<sub>3</sub>), (R<sub>3</sub>, R<sub>4</sub>), (R<sub>4</sub>, R<sub>1</sub>), (C<sub>1</sub>, C<sub>2</sub>), (C<sub>2</sub>, C<sub>3</sub>), (C<sub>3</sub>, C<sub>4</sub>), (C<sub>4</sub>, C<sub>1</sub>)}.

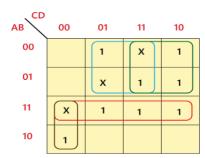

- If w=0, then 4 variable K-map becomes 3 variable K-map. **Example-**  $f(W,X,Y,Z) = \sum m(2,6,8,9,10,11,14,15)$  using K-map.

The given Boolean function is in sum of products form. It is having 4 variables W, X, Y & Z. So, we require **4 variable K-map**.

| WX YZ | 00 | 01 | 11 | 10 |

|-------|----|----|----|----|

| 00    |    |    |    | 1  |

| 01    |    |    |    | 1  |

| 11    |    |    | 1  | 1  |

| 10    | 1  | 1  | 1  | 1  |

The 4 variable K-map with three groupings is

Therefore, the **simplified Boolean function** is **f = WX' + WY + YZ'**

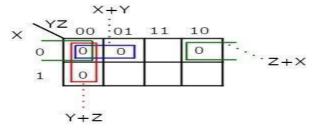

**Example-**  $f(X,Y,Z)=\prod M(0,1,2,4)$  using

K-map.

The given Boolean function is in product of Max terms form. It is having 3 variables X, Y & Z. So, we require 3 variable K-map.

| x YZ | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 0  |    | 0  |

| 1    | 0  |    |    |    |

The 3 variable K-map with three groupings is

Therefore, the simplified Boolean function is

$$f = (X+Y). (Y+Z). (Z+X)$$

#### Don't care condition:

- The "Don't care" condition says that we can use the blank cells of a K-map to make a group of the variables.

- To make a group of cells, we can use the "don't care" cells as either 0 or 1, and if required, we can also ignore that cell.

- We mainly use the "don't care" cell to make a large group of cells.

- The cross(X) symbol is used to represent the "don't care" cell in K-map.

- This cross symbol represents an invalid combination.

- The "don't care" in excess-3 code are 0000, 0001, 0010, 1101, 1110, and 1111 because they are invalid combinations.

- Apart from this, the 4-bit BCD to Excess-3 code, the "don't care" are 1010, 1011, 1100, 1101, 1110, and 1111.

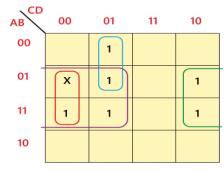

# Example 1: Minimize $f = \sum m(1,5,6,12,13,14) + d(4)$ in SOP minimal form

So, the minimized SOP form of the function is: f

= BC' + BD' + A'C'D **Example-2**:

Minimize the following function in SOP minimal form using K-Maps:  $F(A, B, C, D) = \sum m(1, 2, 6, 7, 8, 13, 14, 15) + d(3, 5, 12)$

F = AC'D' + A'D + A'C + AB

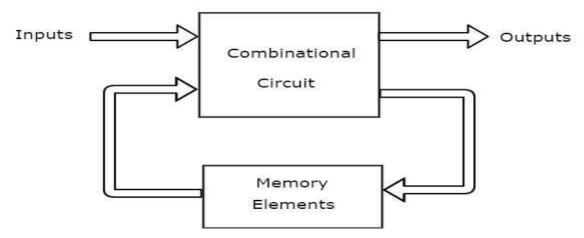

# **UNIT-2Combinational logic circuit**

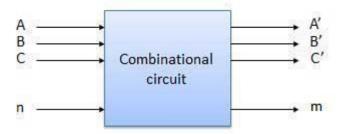

Combinational circuit is a circuit in which we combine the different gates in the circuit, for example encoder, decoder, multiplexer and demultiplexer. Some of the characteristics of combinational circuits are following –

- The output of combinational circuit at any instant of time, depends only on the levels present at input terminals.

- The combinational circuit do not use any memory. The previous state of input does not have any effect on the present state of the circuit.

- A combinational circuit can have an n number of inputs and m number of outputs.

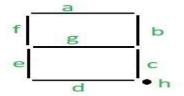

#### Block Diagram:

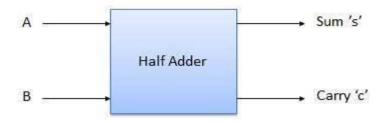

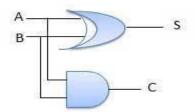

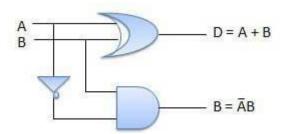

#### **Half Adder**

Half adder is a combinational logic circuit with two inputs and two outputs. The half adder circuit is designed to add two single bit binary number A and B. It is the basic building block for addition of two **single** bit numbers. This circuit has two outputs **carry** and **sum**. Block diagram

Truth Table

| Inpu | ts | Output |

|------|----|--------|

| Α    | В  | s c    |

| 0    | 0  | 0 0    |

| 0    | 1  | 1 0    |

| 1    | 0  | 1 0    |

| 1    | 1  | 0 1    |

# Circuit Diagram

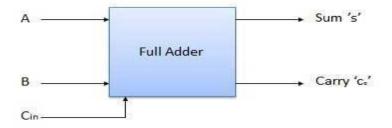

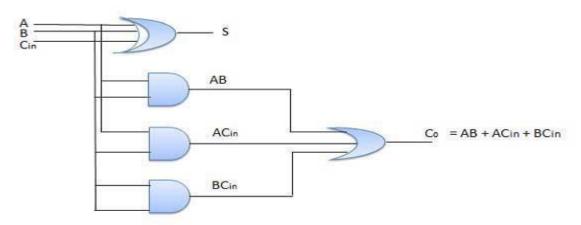

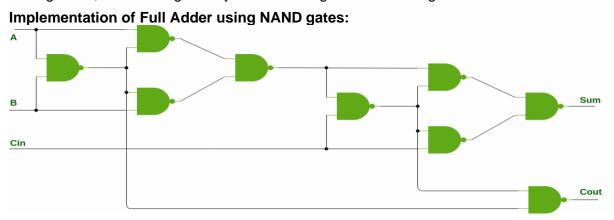

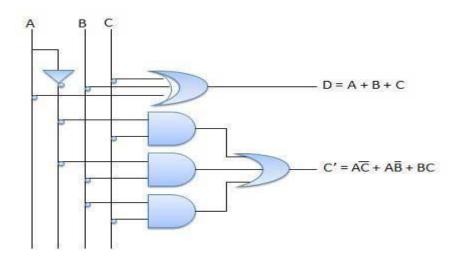

# **Full Adder**

Full adder is developed to overcome the drawback of Half Adder circuit. It can add two onebit numbers A and B, and carry c. The full adder is a three input and two output combinational circuit.

Block diagram

Truth Table

|   | Inputs |     | Output |

|---|--------|-----|--------|

| А | В      | Cin | S Co   |

| 0 | 0      | 0   | 0 0    |

| 0 | 0      | 1   | 1 0    |

| 0 | 1      | 0   | 1 0    |

| 0 | 1      | 1   | 0 1    |

| 1 | 0      | 0   | 1 0    |

| 1 | 0      | 1   | 0 1    |

| 1 | 1      | 0   | 0 1    |

| 1 | 1      | 1   | 1 1    |

# Circuit Diagram

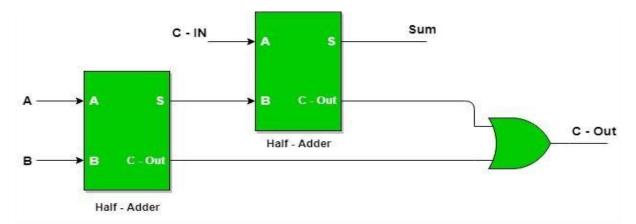

Implementation of Full Adder using Half Adders

2 Half Adders and a OR gate is required to implement a Full Adder.

With this logic circuit, two bits can be added together, taking a carry from the next lower order of magnitude, and sending a carry to the next higher order of magnitude.

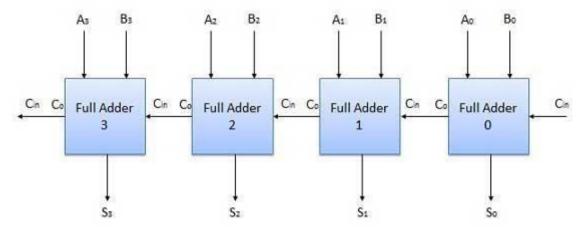

The Full Adder is capable of adding only two single digit binary number along with a carry input. But in practical we need to add binary numbers which are much longer than just one bit. To add two n-bit binary numbers we need to use the n-bit parallel adder. It uses a number of full adders in cascade. The carry output of the previous full adder is connected to carry input of the next full adder.

#### 4 Bit Parallel Adder

In the block diagram,  $A_0$  and  $B_0$  represent the LSB of the four bit words A and B. Hence Full Adder-0 is the lowest stage. Hence its  $C_{in}$  has been permanently made 0. The rest of the connections are exactly same as those of n-bit parallel adder is shown in fig. The four-bit parallel adder is a very common logic circuit.

# Block diagram

#### **Half Subtractors**

Half subtractor is a combination circuit with two inputs and two outputs (difference and borrow). It produces the difference between the two binary bits at the input and also produces an output (Borrow) to indicate if a 1 has been borrowed. In the subtraction (A-B), A is called as Minuend bit and B is called as Subtrahend bit.

# Truth Table

| Inpu | its | Output  |        |

|------|-----|---------|--------|

| Α    | В   | (A - B) | Borrow |

| 0    | 0   | 0       | 0      |

| 0    | 1   | 1       | 1      |

| 1    | 0   | 1       | 0      |

| 1    | 1   | 0       | 0      |

# Circuit Diagram

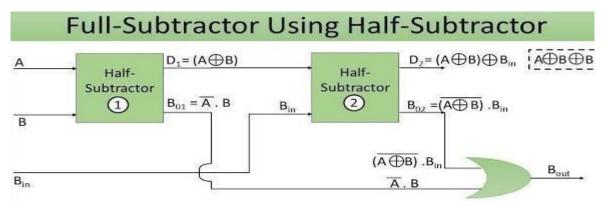

#### **Full Subtractors**

The disadvantage of a half subtractor is overcome by full subtractor. The full subtractor is a combinational circuit with three inputs A,B,C and two output D and C'. A is the 'minuend', B is 'subtrahend', C is the 'borrow' produced by the previous stage, D is the difference output and C' is the borrow output.

# Truth Table

|   | Input | 5 | Output  |    |

|---|-------|---|---------|----|

| Α | В     | С | (A-B-C) | C, |

| 0 | 0     | 0 | 0       | 0  |

| 0 | 0     | 1 | 1       | 1  |

| 0 | 1     | 0 | 1       | 1  |

| 0 | 1     | 1 | 0       | 1  |

| 1 | 0     | 0 | 1       | 0  |

| 1 | 0     | 1 | 0       | 0  |

| 1 | 1     | 0 | 0       | 0  |

| 1 | 1     | 1 | 1       | 1  |

# Circuit Diagram

# **Multiplexers**

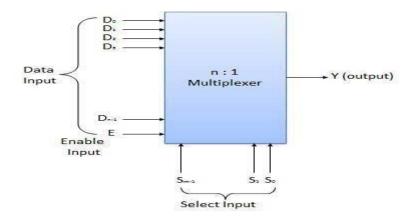

Multiplexer is a special type of combinational circuit. There are n-data inputs, one output and m select inputs with 2m = n. It is a digital circuit which selects one of the n data inputs and routes it to the output. The selection of one of the n inputs is done by the selected inputs. Depending on the digital code applied at the selected inputs, one out of n data sources is selected and transmitted to the single output Y. E is called the strobe or enable input which is

useful for the cascading. It is generally an active low terminal that means it will perform the required operation when it is low.

# Block diagram

# Multiplexers come in multiple variations

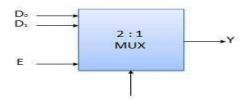

2:1 multiplexer

• 4:1 multiplexer

• 16:1 multiplexer

• 32:1 multiplexer

# **Block Diagram**

Truth Table

| Enable | Select | Output         |

|--------|--------|----------------|

| E      | S      | Υ              |

| 0      | x      | 0              |

| 1      | 0      | Do             |

| 1      | 1      | D <sub>1</sub> |

x = Don't care

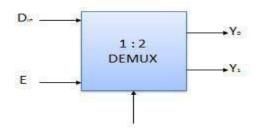

# **Demultiplexers**

A demultiplexer performs the reverse operation of a multiplexer i.e. it receives one input and distributes it over several outputs. It has only one input, n outputs, m select input. At a time only one output line is selected by the select lines and the input is transmitted to the selected output line. A de-multiplexer is equivalent to a single pole multiple way switch as shown in fig.

Demultiplexers comes in multiple variations.

• 1:2 demultiplexer

• 1:4 demultiplexer

• 1:16 demultiplexer

• 1:32 demultiplexer

# Block diagram

Truth Table

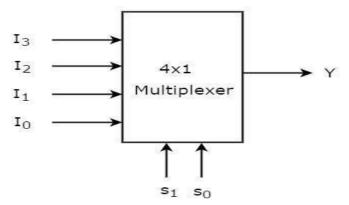

# 4:1 Multiplexer

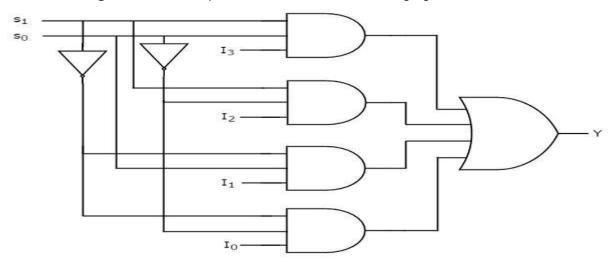

4:1 Multiplexer has four data inputs  $I_3$ ,  $I_2$ ,  $I_1$ &  $I_0$ , two selection lines  $s_1$ &  $s_0$  and one output Y. The **block diagram** of 4x1 Multiplexer is shown in the following figure.

One of these 4 inputs will be connected to the output based on the combination of inputs present at these two selection lines.

**Truth table** of 4:1 Multiplexer is shown below.

| Selection Lines |                | Output         |

|-----------------|----------------|----------------|

| S <sub>1</sub>  | S <sub>0</sub> | Y              |

| 0               | 0              | I <sub>0</sub> |

| 0 | 1 | I <sub>1</sub> |

|---|---|----------------|

| 1 | 0 | l <sub>2</sub> |

| 1 | 1 | l <sub>3</sub> |

From Truth table, we can directly write the Boolean function for output, Y as

$$Y = S1'S0'I_0 + S1'S0I_1 + S1S0'I_2 + S1S0I_3$$

We can implement this Boolean function using Inverters, AND gates & OR gate.

The **circuit diagram** of 4:1 multiplexer is shown in the following figure.

We can easily understand the operation of the above circuit. Similarly, you can implement 8x1 Multiplexer and 16x1 multiplexer by following the same procedure.

| Enable | Select | Output |     |

|--------|--------|--------|-----|

| E      | S      | YO     | Y1  |

| 0      | x      | 0      | 0   |

| 1      | 0      | 0      | Din |

| 1      | 1      | Din    | 0   |

x = Don't care

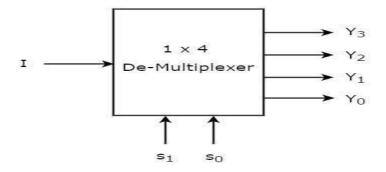

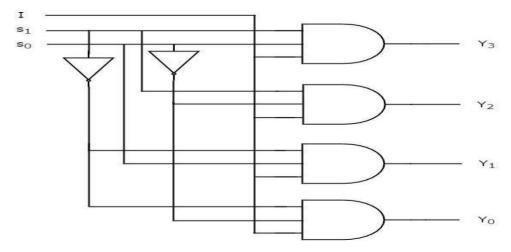

# 1:4 De-Multiplexer

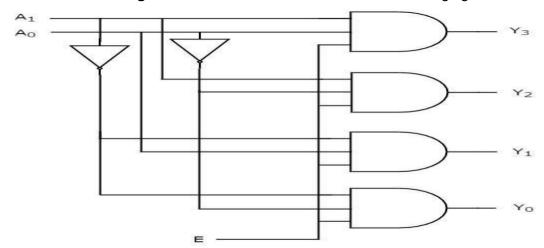

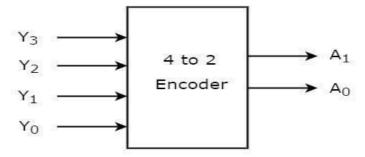

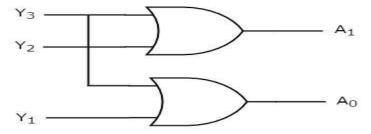

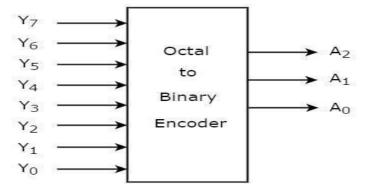

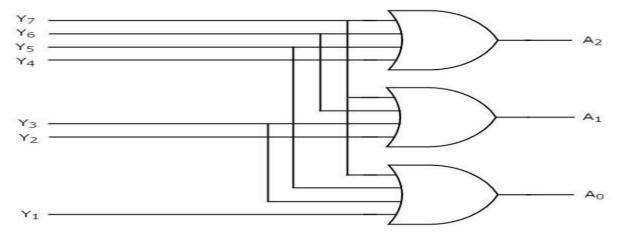

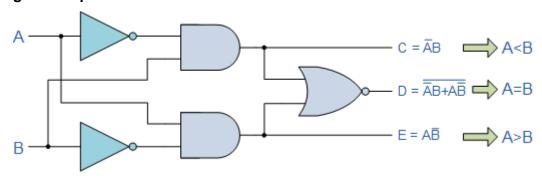

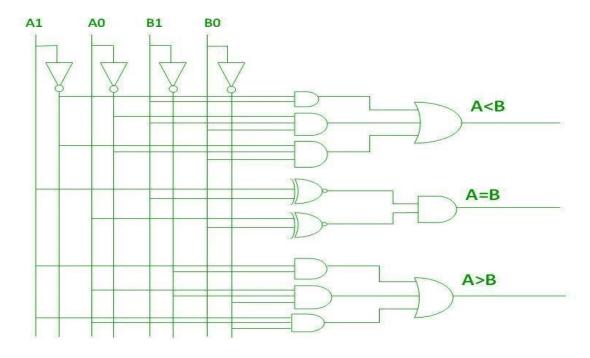

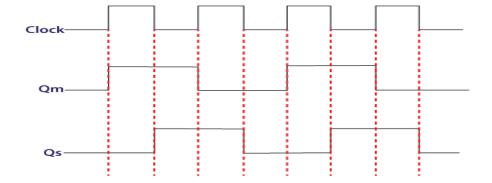

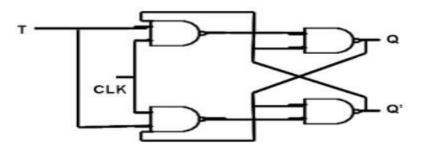

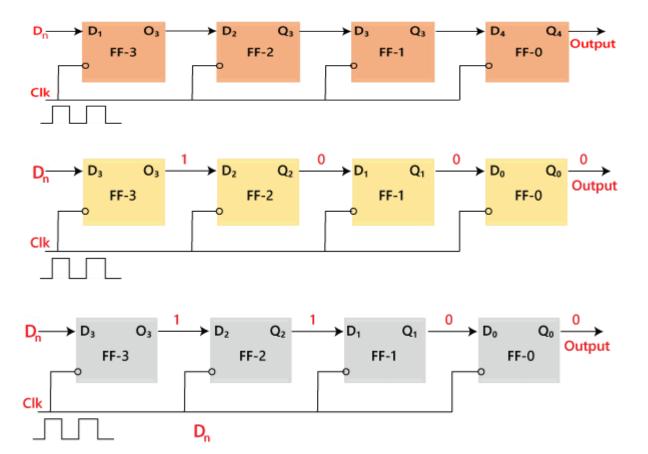

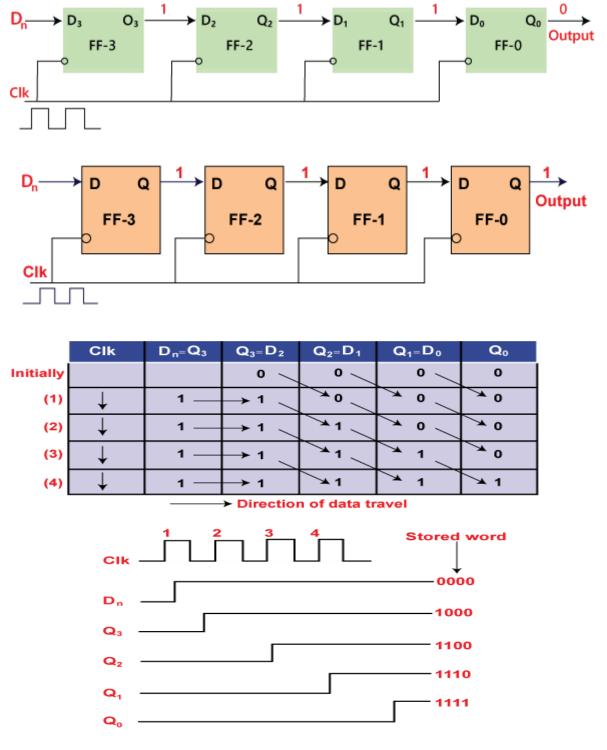

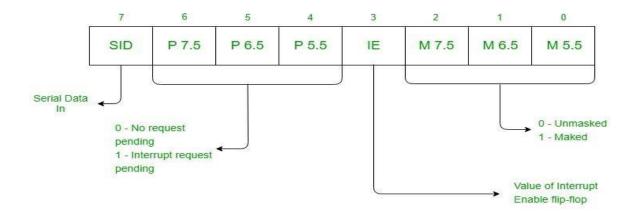

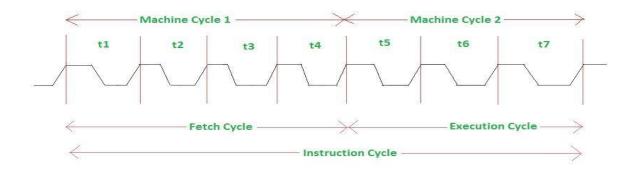

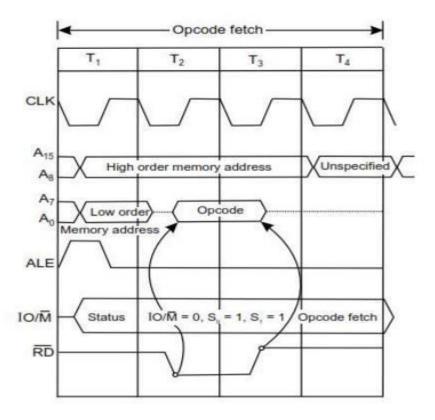

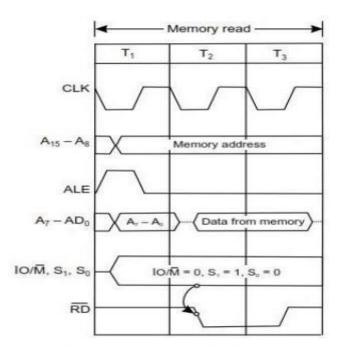

1:4 De-Multiplexer has one input I, two selection lines,  $s_1$ &  $s_0$  and four outputs  $Y_3$ ,  $Y_2$ ,  $Y_1$ & $Y_0$ . The **block diagram** of 1:4 De-Multiplexer is shown in the following figure.